The Core of Powerful, Power-Efficient Processors

Team from UC San Diego and HP Labs has been honored with a Test of Time award for creating a novel processor architecture

By:

- Katie E. Ismael

Published Date

By:

- Katie E. Ismael

Share This:

Article Content

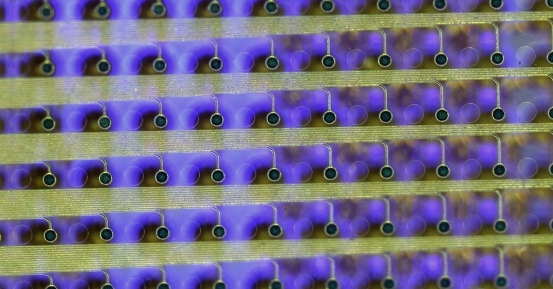

The high-performance yet low-power processors running billions of today’s laptops and mobile devices come thanks to research by computer scientists at the University of California San Diego and HP Labs.

Their work, which began nearly two decades ago, has influenced the design of many modern processors such as ARM's big.Little, Qualcomm’s Snapdragon, Intel's Alder Lake and Apple’s flagship Apple M1, including the recently announced M1Pro and M1 Max.

“Nearly everyone probably has one running something in their lives,” said Dean Tullsen, a UC San Diego Computer Science and Engineering professor who was part of the team who set the foundation for a new way of thinking about processors.

Now, the paper that led to a novel processor architecture that would provide significant energy benefits has been recognized for its lasting impact with a MICRO Test of Time Award.

The paper, “Single-ISA Heterogenous Multi-Core Architectures: The Potential for Processor Power Reduction” published in 2003, has since been cited more than 1,000 times and spawned several impactful academic and industrial projects on heterogeneous systems.

“This simple, but powerful idea now drives a large number of computer systems,” said Luiz Barroso, a Google Fellow and head of the Office of Cross-Google Engineering, who nominated the paper.

At the time their paper was published, processors were increasing in performance and speed, resulting in challenges with power consumption and heat dissipation in designing future high-performance systems.

Multicores, which mean more than one processor core on a single chip, were

just starting to enter the market. However, all commercial designs, and in fact all roadmaps from the processor vendors, assumed all cores were identical (as virtually all multi-chip multiprocessors had been before that). The team challenged that assumption and pointed out that if the cores were different, they could better address the variation in program behavior and changes in environment.

They proposed a new architecture for processors that would switch among cores to optimize energy and performance. Their multi-core model would allow software to evaluate the resource requirements of an application (or part of an application) and choose the core that would best meet the requirements while minimizing energy consumption.

“Contrary to homogeneous multi-cores, which were state-of-art then, the paper showed that putting cores with different power-performance characteristics on the same die with intelligent application mapping produces large improvements in energy efficiency,” said Barroso.

Powerful Collaborations

The paper’s lead author, Rakesh Kumar, then a Ph.D. student in the Department of Computer Science and Engineering who was being mentored by Tullsen, took a summer internship at HP Labs to begin the project. Kumar and Tullsen formed a partnership with Norman Jouppi, Parthasarathy Ranganathan, and Keith Farkas from HP.

The team continued their research for several years, publishing seven papers on the topic. This turned out to be quite an influential group, as they went on to amass numerous Test of Time awards on various topics: five for Tullsen, four for Norman Jouppi of HP Labs (now Google), and two for Kumar, who is now an associate professor at University of Illinois, Urbana-Champaign. Ranganathan is currently a vice president at Google and Farkas is currently with VMWare.

“This ended up being one of my favorite research projects ever,” said Tullsen. “Not just because of the widespread impact it had, but because of the amazing group of people I got to work with.”

Share This:

You May Also Like

Stay in the Know

Keep up with all the latest from UC San Diego. Subscribe to the newsletter today.